巨头们的先进封装技术解读

来源:本文由半导体行业观察(ID:icbank)编译自semianalysis,感谢分享。

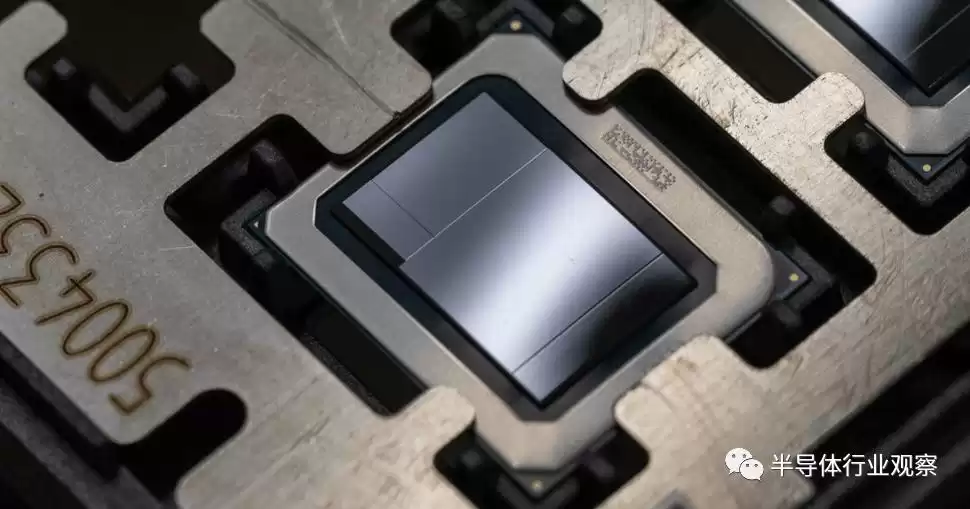

你知道吗?在上一篇《先进封装最强科普》中,我们只是浅尝辄止地讨论了市场对先进封装的需求。但今天,让我们聚焦于巨头们的实战技术——无论是英特尔的EMIB、Foveros系列,台积电的InFO和CoWoS平台,三星的FOSiP和X-Cube,还是ASE、索尼、美光等公司的创新,它们的封装方案各显神通,正被AMD、Nvidia等巨头广泛应用于高性能产品中。

在本文中,我们将逐一拆解这些封装技术的核心原理与应用场景,带你看清技术背后的竞争格局。

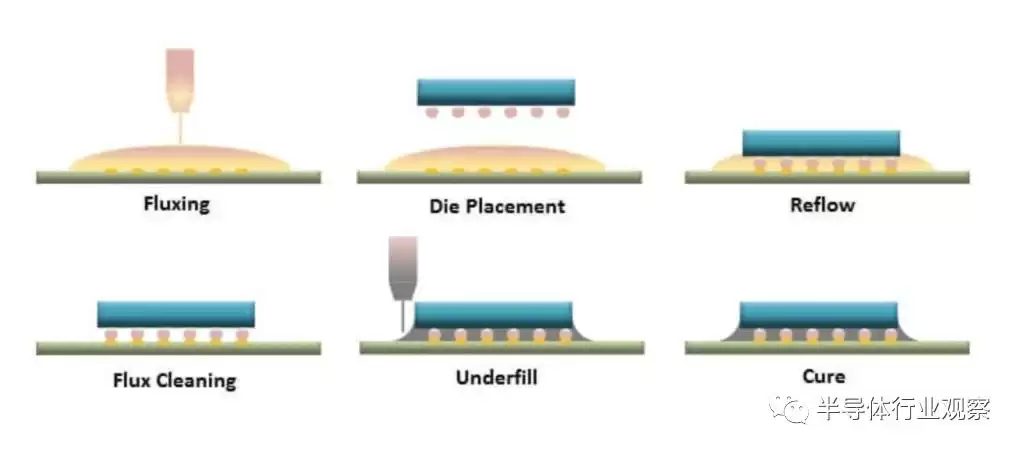

倒装芯片作为引线键合后的主流封装形式,被代工厂和OSAT公司广泛采用。想象一下:在PCB或基板上,芯片通过凸块精准对接焊盘,经回流焊加热融合,再填充底部材料——这一流程虽基础,却衍生出多种高级变体,如无助焊剂工艺,展现出封装技术的多样性。

尽管倒装芯片普及,但间距小于100微米的高级版本却鲜见。只有台积电、三星、英特尔等少数巨头能驾驭此类技术,它们通过逻辑先进封装推动芯片性能飞跃。这些公司中,部分自研硅片,另一些则专注外包测试,形成互补生态。

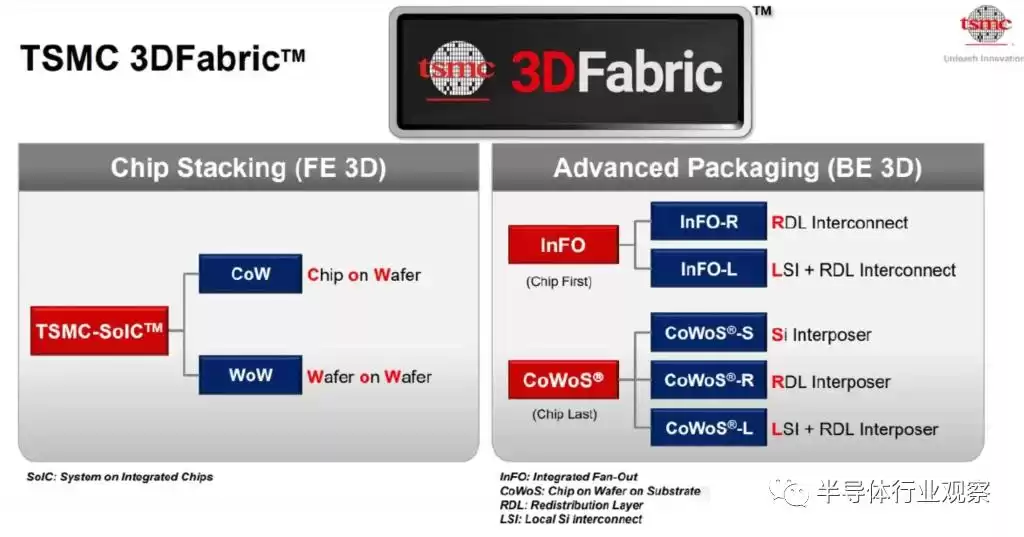

随着尺寸缩小,封装类型百花齐放。以台积电为例,其技术差异关键在于基板材料、尺寸和堆叠方式。我们将对比其他公司的方案,揭示技术路径的多样性。

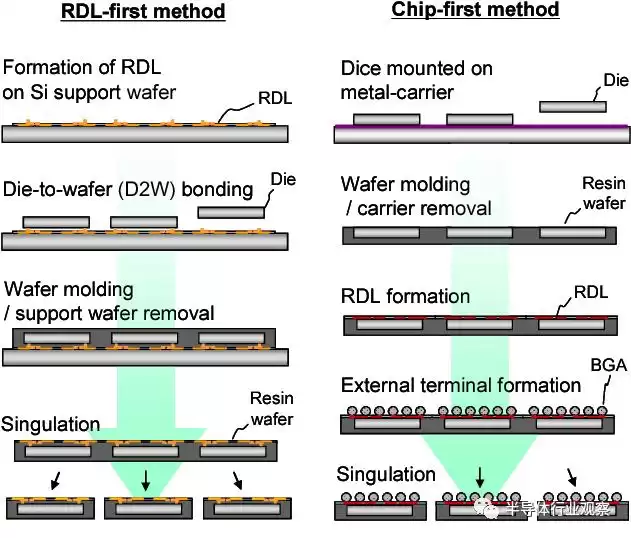

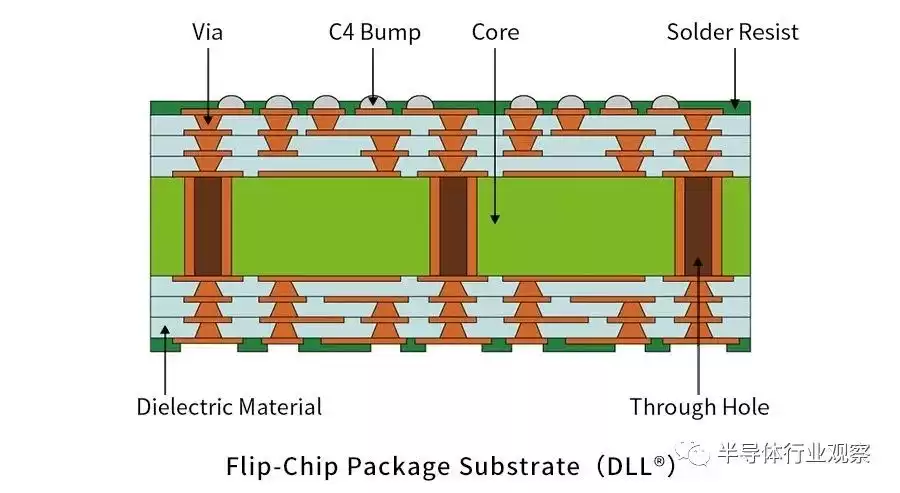

标准倒装芯片常用有机层压板基板,覆铜后通过ABF薄膜构建布线层。这些层利用干膜层压和激光技术成型,负责信号重分配。但台积电的集成扇出(InFO)另辟蹊径,采用光刻工艺定义再分布层,实现更高密度布线,适用于复杂场景如智能手机和AI加速器。

台积电的InFO技术凸显其制造优势:通过光刻工具打造精细RDL,比OSAT方案更紧凑。ASE的FoCoS和三星的FOSiP也类似,服务于移动和汽车领域。例如,苹果芯片和思科交换机ASIC均受益于此,推动封装向更大尺寸、更高功耗演进。

InFO-R支持高IO密度和多芯片集成,助力产品如iPhone和网络交换机。三星则凭借思科Silicon One抢占市场,技术竞争白热化。

传闻AMD Zen 4 CPU将采用扇出封装,已获确认。这种设计将扇出置于有机基板上,提升性能的同时降低成本,后续我们将揭秘技术细节。

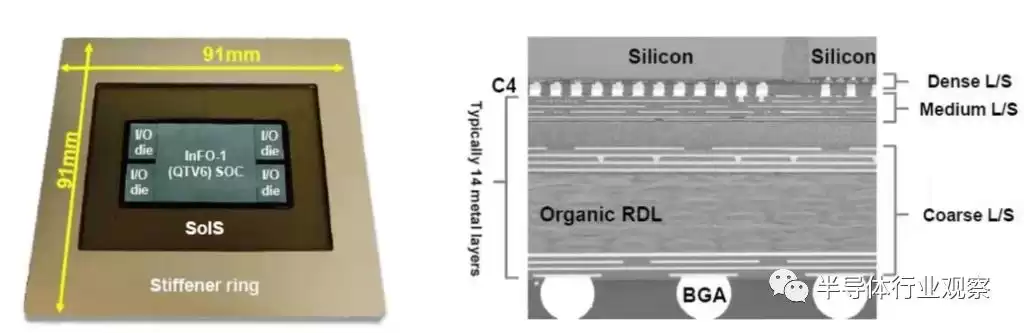

标准封装仅有少数RDL层,但台积电InFO-SoIS多达14层,实现芯片间复杂互联。靠近芯片的高密度布线进一步优化性能,适用于高端计算场景。

台积电InFO-SOW更突破性地支持晶圆级封装,如特斯拉Dojo 1系统,实现超大规模集成。三星FOSiP也将用于特斯拉HW 4.0,展现技术跨界应用。

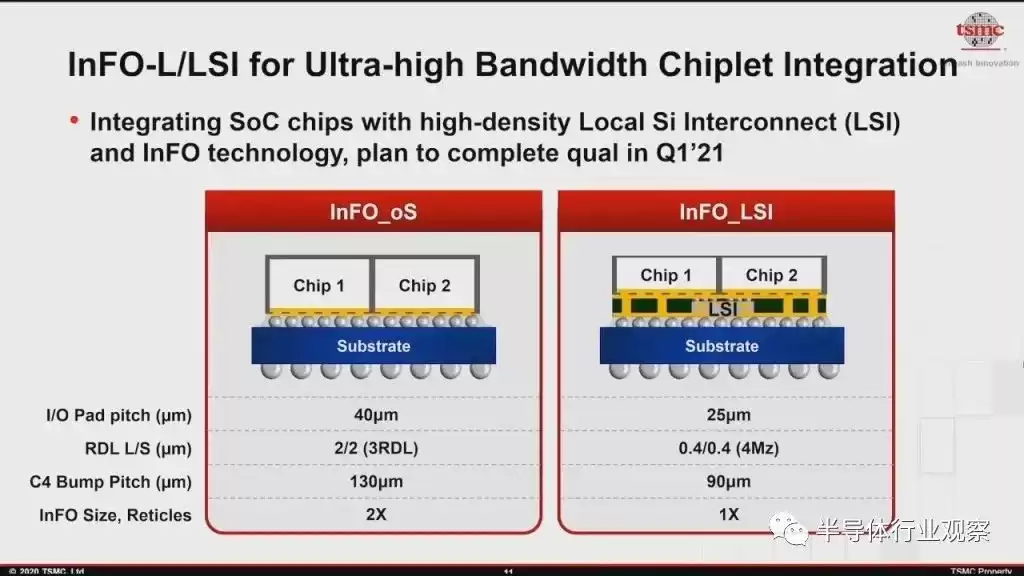

台积电InFO-LSI在芯片下加入硅互连,未来可演变为有源层。相比英特尔EMIB,它更接近Foveros Omni或ASE FOEB,凸显材料选择差异。

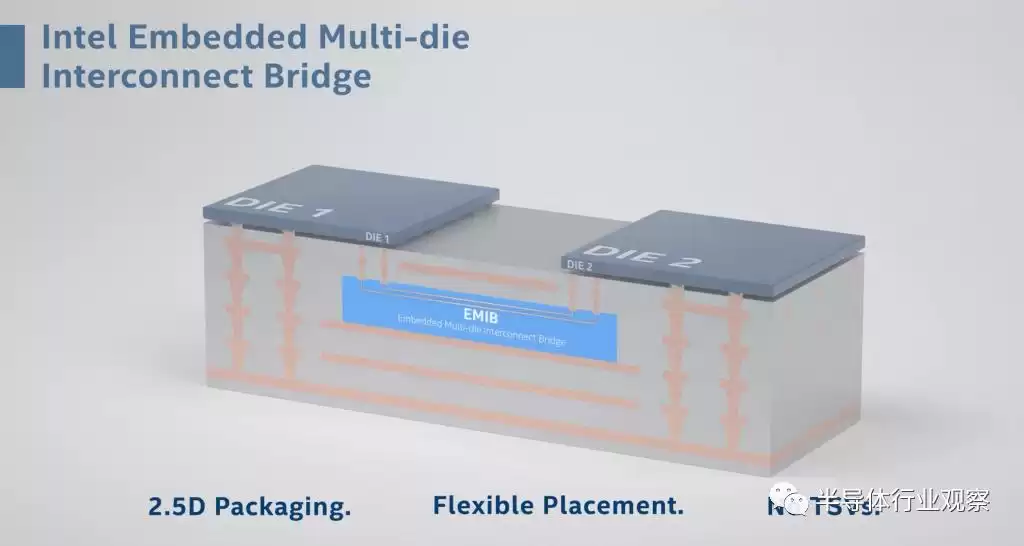

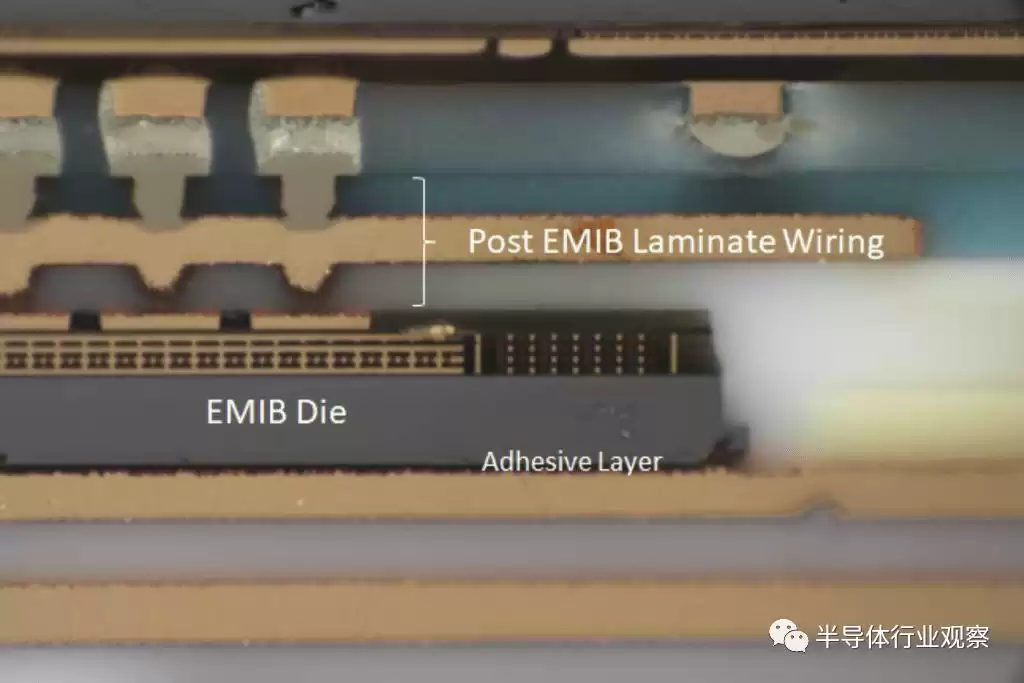

英特尔EMIB嵌入有机基板,利用商品化供应链降低成本。自2018年用于FPGA和GPU后,其间距从55微米缩至40微米,支持灵活设计,如可选的芯片配置,优化BOM。

EMIB通过硅桥推送功率,并可省略无需部件,节省成本。与台积电CoWoS的全硅桥对比,EMIB在材料和工艺上更经济。

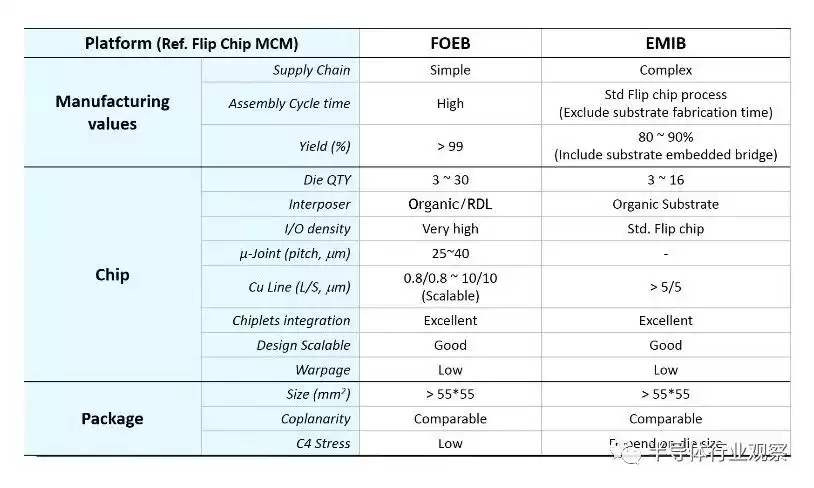

ASE的FOEB技术用于AMD MI200 GPU,类似台积电InFO-LSI,但采用玻璃基板降低成本。通过扇出和光刻RDL,它在布线密度上占优,尽管成本较高。

FOEB先建铜柱和RDL,再键合芯片,移除玻璃中介层后封装。与EMIB近100%的良率相比,FOEB虽贵却更精密,反映ASE以价换市的策略。

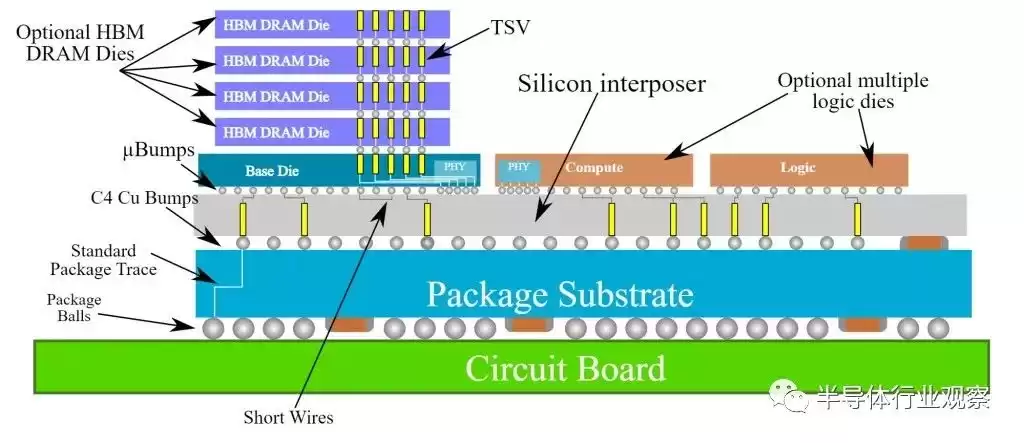

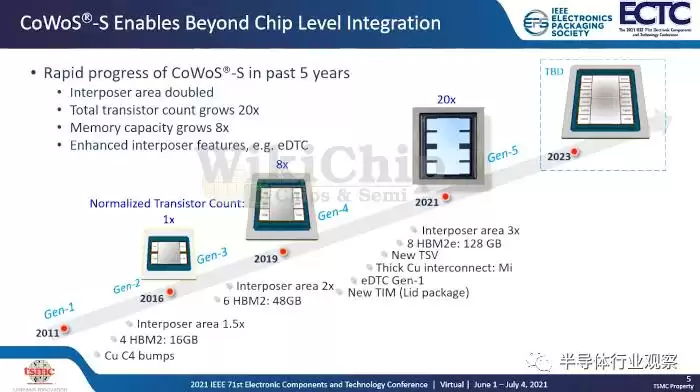

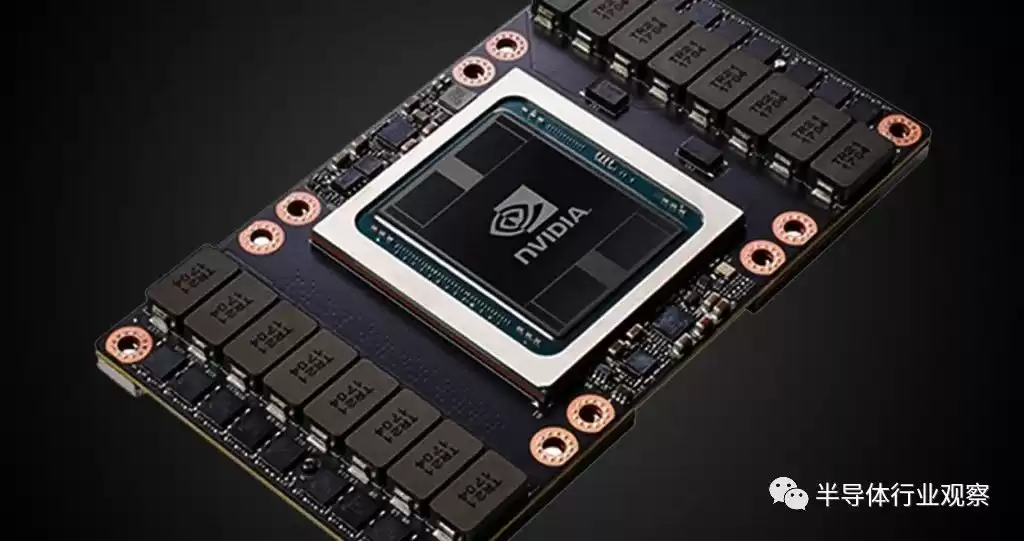

台积电的CoWoS平台包括CoWoS-R和CoWoS-L,与InFO对应,区别在于工艺顺序。CoWoS-S作为主力,通过硅中介层连接芯片和HBM,广泛应用于Nvidia GPU等高性能芯片。

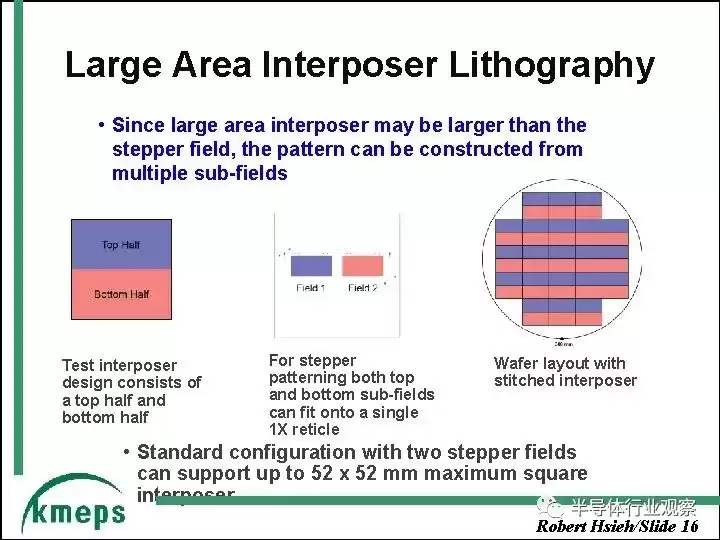

CoWoS-S需求火爆,英伟达预付巨资抢占产能。其中介层面积通过光罩拼接突破限制,达3倍标尺,但EMIB等技术避免了高成本问题。

技术演进包括铜凸块和TIM封装优化,解决如英伟达GPU散热问题。三星I-Cube类似但客户较少,如百度AI芯片。

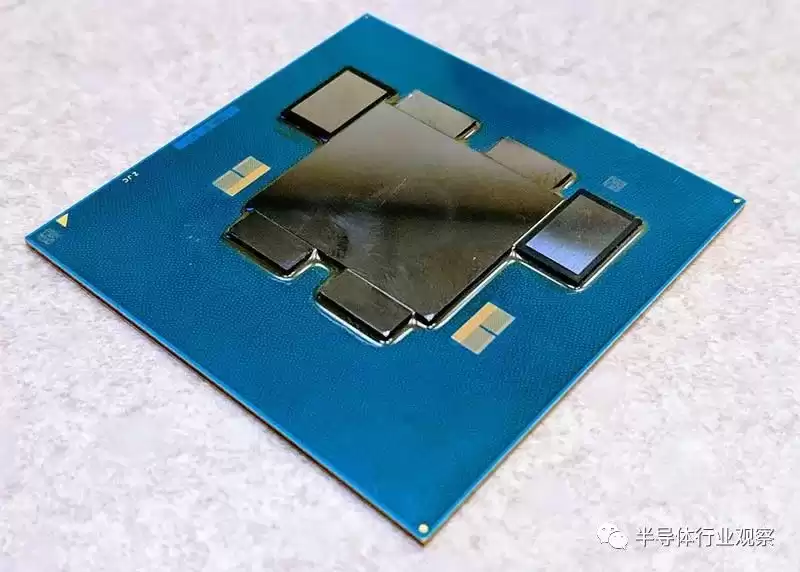

英特尔Foveros实现3D堆叠,如Lakefield CPU,间距55微米。Ponte Vecchio GPU用36微米间距,未来客户端产品将普及此技术。

Foveros Omni作为桥接技术,支持多向互联,通过铜柱适应不同高度。DRAM如HBM也用先进封装,SK海力士引入混合键合提升集成度。

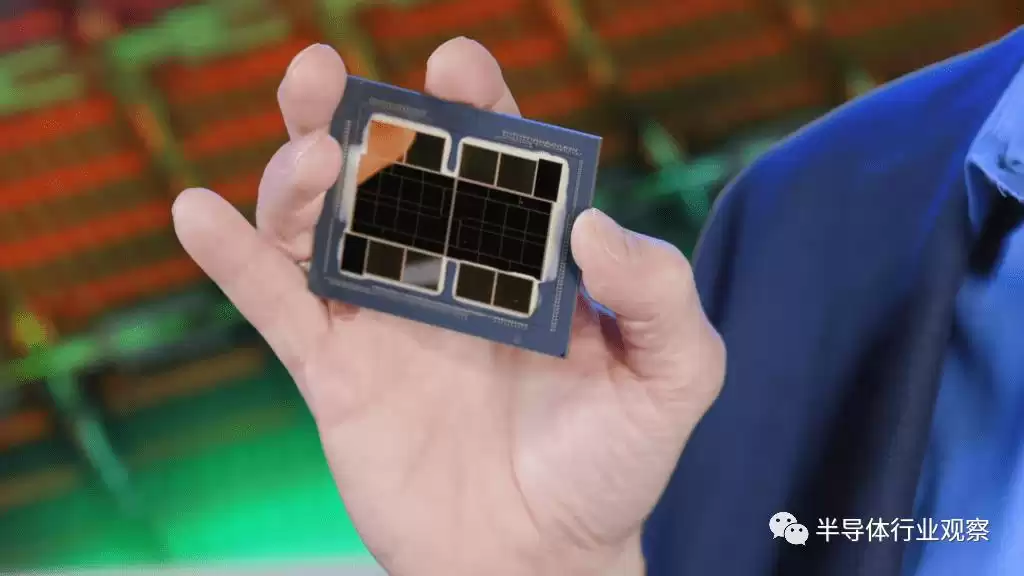

混合键合直接铜-铜连接,无需凸块,实现更高密度。AMD 3D缓存用台积电SoIC,索尼CMOS传感器已大规模应用,间距低至6.3微米。

索尼和三星主导混合键合市场,长江存储Xtacking用于NAND,提升单元密度。工具生态多样,但赢家未定,下篇将深入探讨。

★ 点击文末【阅读原文】,可查看本文原文链接!

免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2913内容,欢迎关注。

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

原文链接!

相关问答

芯片封装三大技术差异解析-ZOL问答

倒装焊、载带自动焊和引线键合是三种常见芯片封装技术。倒装焊多用于高性能芯片,载带自动焊适用于大规模生产,引线键合成本低应用广泛。目前引线键合使用最多...

芯片封装与光刻区别?

芯片封装和光刻是半导体制造过程中的两个不同步骤。1.芯片封装(ChipPackaging):芯片封装是将制造好的芯片(即在硅晶圆上制造的集成电路)进行包装和封装,...

4nm手机芯片封装技术高吗?

比较高,但不是最高。4nm手机芯片封装技术属于高端芯片的封装技术,但在整个芯片制造环节中属于后道工序,技术程度远不如前道光刻技术。芯片封装就是给加工好的...

CPU封装是什么意思?不同的封装技术有什么区别吗?-ZOL问答

不同的封装技术有什么区别吗?CPU封装是什么意思?不同的封装技术有什么区别吗?CPU讨论回答(6)gjm1974所谓“封装技术”是一种将集成电路用绝缘的塑料或陶瓷...

芯片行业有含金量的证书?

芯片行业是有含金量比较高的证书如考FPGA工程师等。芯片几乎在任何行业都广泛地使用,有些生产制造企业必须大量使用具有高级功能包含芯片的机器设备,在许多情...

PCB线路板中的倒装芯片(FlipChip)是什么?-ZOL问答

6条回答:倒装芯片位于PCB线路板上,是其中一种芯片类型,Flipchip属于芯片封装形式,用于电路连接。倒装封装(Flipchip)属于晶圆级封装,不同于传统方式。它并非先将...

中国半导体芯片制造有哪些技术瓶颈?-ZOL问答

半导体芯片犹如现代工业的心脏一般重要。随着人类即将步入由AI所引领的第四次工业革命,芯片的重要性愈发显著。接下来,我们简要梳理一下芯片制造的各个环节...

CPU封装方式有哪几种?-ZOL问答

封装技术就是把集成电路用塑料或陶瓷包起来的一种方法。拿CPU来说,咱们看到的那个大小和样子,其实不是真正的CPU核心的样子,而是封装之后的样子。封装对芯片来...

Chiplet是什么?为何被称为跨越摩尔定律的技术路径?-ZOL问答

Chiplet本质上是一种设计理念,它通过封装和互联技术,将采用不同工艺、具备不同功能的模块化小芯片(芯粒)像拼接乐高积木一样整合在一起,最终形成一个完整的芯片...

BGA封装的IC要用什么工具和焊接技术拆装?-ZOL问答

要看芯片的大小而定,小的芯片(例如手机的)可以直接用热风枪就能拆焊,大的芯片(例如电脑的)因为芯片太大,用热风枪加热受热不均匀,很难拆下来,必要用到专门的BGA...